# Architecture des processeurs VLSI

F. Anceau Département d'Informatique

Septembre 1997

#### Résumé

Les microprocesseurs représentent l'un des plus importants phénomènes techniques de cette fin de XX siècle. Depuis près de vingt-cinq ans, leur puissance de calcul et leur complexité n'ont cessé de croître à un rythme soutenu. Ces dispositifs électroniques jouent un rôle de plus en plus important dans la société moderne. En particulier, ceux que nous qualifierons d"'invisibles" sont utilisés pour conduire et observer des machines outils, des automobiles, des avions, des appareils électroménagers et beaucoup d'autres appareils. Ce sont de loin les plus nombreux. Leur présence change progressivement la relation que nous avons avec ces objets. D'un point de vue économique, il est intéressant de montrer que le phénomène microprocesseur est plus "trié par le marché" plutôt que "poussé par la technologie". La réalisation micro-électronique de ces dispositifs représente un enjeu continu pour les concepteurs et les technologues qui s'efforcent de réaliser les produits que désire le marché et qui sont généralement planifiés longtemps à l'avance. Les microprocesseurs monolithiques sont en train de prendre le pas sur tous les autres types d'ordinateurs. La gamme des mini-ordinateurs a été "absorbée" pendant les années 80, les machines de centre de calcul sont en train de l'être et probablement la gamme des super-ordinateurs va aussi l'être dans la première décennie du siècle prochain. Tout au long de leur extraordinaire évolution, ces dispositifs ont réutilisé toutes les innovations techniques qui ont été développées pour les précédentes générations d'ordinateurs. Le futur des microprocesseurs comporte un extraordinaire défi: Le maintient du rythme d'évolution de la puissance de calcul tout en assurant une stricte compatibilité binaire demande l'invention de nouvelles méthodes d'exécution ainsi que le franchissement du "mur quantique" vers 2010.

Copyright © 1997, 1998. La copie de tout ou partie de ce document est autorisée pour une utilisation personnelle, de recherche ou d'enseignement, avec mention explicite de l'auteur. Toute autre utilisation nécessite une autorisation écrite de celui-ci.

# TABLE DES MATIERES

| 1 INTRODUCTION                                                      | 3  |

|---------------------------------------------------------------------|----|

| 2 UN RYTHME D'EVOLUTION SOUTENU                                     | 3  |

| 3 LES PROCESSEURS VLSI VUS COMME DES PRODUITS DE GRANDE CONSOMATION | 4  |

| 4 UN REGARD VERS LE FUTUR                                           | 5  |

| 5 ABSORPTION DES GAMMES D'ORDINATEURS PAR LES MICROPROCESSEURS      | 6  |

| 6 LES MICROPROCESSEURS CHANGENT NOTRE ENVIRONNEMENT                 | 6  |

| 7 L'HERITAGE DES ORDINATEURS                                        | 6  |

| 8 LES MICROPROCESSEURS VUS COMME DES CIRCUITS VLSI                  | 7  |

| 9 LES PROCESSEURS VUS COMME DES INTERPRETEURS                       | 7  |

| 10 CONCEPTION DU CHEMIN DE DONNEES                                  | 8  |

| 11 CONCEPTION DE LA PARTIE COMMANDE                                 | 8  |

| 12 PROCESSEURS RISC                                                 | 9  |

| 13 ACCELERATION DE L'EXECUTION                                      | 10 |

| 14 EXECUTION PIPELINE                                               | 10 |

| 15 REGISTRES VIRTUELS                                               | 11 |

| 16 PREDICTION DES BRANCHEMENTS                                      | 11 |

| 17 TECHNIQUES STATIQUES DE PREDICTION                               | 11 |

| 18 TECHNIQUES DE PREDICTION DYNAMIQUES                              | 11 |

| 19 AUTRES TECHNIQUES COMPLEMENTAIRES                                | 12 |

| 20 SUPER-PIPELINE                                                   | 12 |

| 21 SUPER-SCALAIRE                                                   | 12 |

| 22 EXECUTION DANS LE DESORDRE                                       | 13 |

| 23 TRADUCTION CISC EN RISC                                          | 13 |

| 24 UTILISATION DE TRES LONG MOTS D'INSTRUCTION (VILW)               | 14 |

| 25 AMELIORATION DES ACCES MEMOIRES                                  | 14 |

| 26 HIERARCHIE MEMOIRE                                               | 14 |

| 27 MULTIPROCESSEURS MONOLITHIQUES                                   | 14 |

| 28 CONCLUSIONS                                                      | 14 |

| 29 BIBLIOGRAPHIE                                                    | 15 |

## 1 INTRODUCTION

L'histoire des microprocesseurs (que nous appellerons processeurs VLSI) débute en 1972 avec l'Intel 4004. Celui-ci a été initialement conçu pour réaliser des calculatrices mais il fut utilisé pour beaucoup d'autres applications. Depuis cette époque, les microprocesseurs sont devenus des machines puissantes qui sont en train de prendre le pas sur tous les autres types d'ordinateurs. Ces processeurs VLSI représentent l'un des plus important phénomènes techniques de cette fin de siècle.

#### 2 UN RYTHME D'EVOLUTION SOU TENU

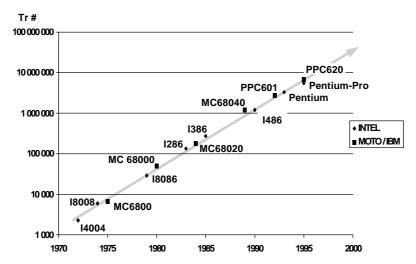

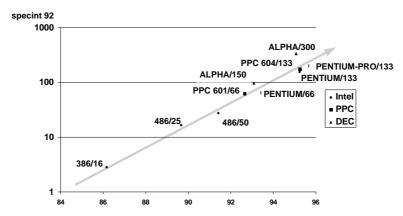

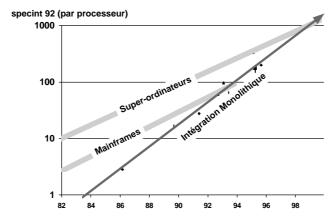

Depuis plus d'un quart de siècle les processeurs VLSI se développent à un rythme soutenu. La complexité de ces circuits augmente régulièrement avec un rythme moyen de 37% par an tandis que leurs performances (mesurées avec un outil d'évaluation commun) se développent à la même vitesse.

Figure 1 Evolution de la complexité des microprocesseurs

Figure 2 Evolution de la performance des microprocesseurs.

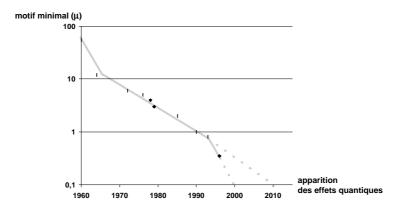

L'évolution de la complexité de ces circuits est très régulière, montrant ainsi l'évolution de la technologie VLSI. La dimension des motifs technologiques minimaux diminue régulièrement tandis que la taille des puces augmente.

Figure 3 Evolution technologique.

Tous les spécialistes prédisent un ralentissement du rythme d'évolution technologique compte tenu de l'extrême difficulté qu'il y a à produire ces circuits. A la surprise générale, il semble que depuis trois ans ce rythme se soit en fait accéléré. La taille des motifs minimaux des meilleures technologies fait actuellement  $0.35\mu m$  au lieu des  $0.45\mu m$  qui seraient dus à une continuation rythme précédent.

A cette vitesse d'évolution, les phénomènes quantiques, qui apparaîtrons autour de  $0.1\mu m$ , devraient se manifester vers 2010 provoquant une dégradation sévère du comportement des transistors MOS classiques.

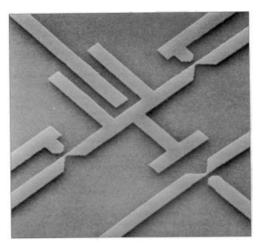

La pression économique est si élevée qu'il existe une bonne chance de briser ce "mur quantique" avant cette date. Déjà, quelques transistors "quantiques" commencent à fonctionner dans des laboratoires de recherche.

Figure 4 Mémoire mono-électron (laboratoire Hitachi, Cambridge, Angleterre).

# 3 LES PROCESSEURS VLSI VUS COMME DES PRODUITS DE GRANDE CONSOMATION

D'un point de vue économique, les microprocesseurs sont à l'origine de la démocratisation de l'informatique. Ils ont contribués à la chute du prix des ordinateurs en réduisant le coût de leur électronique. Ils sont à l'origine du phénomène des ordinateurs individuels. Le marché de ces machines domine maintenant toute l'industrie informatique. L'ampleur de leurs séries est loin au dessus des meilleures ventes d'ordinateur de centre de calcul et même de machines UNIX. L'industrie des ordinateurs individuels est maintenant une industrie de masse produisant des biens de consommation courante.

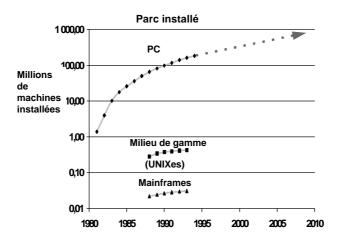

Figure 5 Nombre d'ordinateurs installés.

Vers 1985 le marché des processeurs VLSI s'est transformé depuis un marché mut par l'évolution technologique vers un marché tiré par la demande des clients finaux qui souhaitent en permanence utiliser les dernières versions des produits logiciels. Ceci les conduit à acheter des modèles de plus en plus performants d'ordinateurs individuels pour faire tourner ces programmes. La taille de ce marché est si importante qu'une grande quantité d'argent est disponible pour l'amélioration de la technologie. L'organisation de la production s'inspire des techniques de production de masse comme l'électronique grand public.

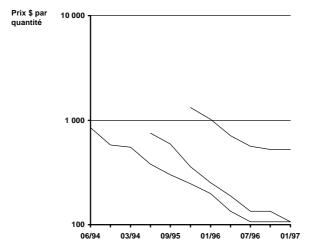

Comme pour tous les circuits VLSI produits en grande série, le prix des microprocesseurs suit une courbe rapidement décroissante partant d'un prix d'introduction de 1000\$ pour aboutir quelques années après vers 100\$. Il est toujours difficile d'admettre que le prix d'un nouveau modèle considéré comme extraordinaire va chuter bientôt jusqu'au niveau de celui d'un produit de grande consommation..

Figure 6 Evolution du prix des microprocesseurs.

# 4 UN REGARD VERS LE FUTUR

La précision des courbes qui montrent l'évolution de la complexité et de la performance des microprocesseurs est relativement bonne. Il est possible de les utiliser pour prédire avec une assez bonne précision les caractéristiques d'un futur processeur VLSI. Toutefois il est plus difficile de prévoir son architecture interne car le prolongement de ces courbes vers le futur représente en fait l'enjeu économique posé par le marché aux concepteurs de microprocesseurs.

Si nous prolongons ces courbes jusque vers 2010 (Jusqu'au mur quantique), le résultat est vraiment impressionnant. A cette date nous devrions disposer de microprocesseurs ayant une complexité d'environ 1 Gtr et une performance autour de 100 Ginstr./s (10 0 Gips).

Il semble difficile de croire de telles prédictions. Pourtant, si nous faisons un retour en arrière pour revenir nous situer en 1986 nous aurions des difficultés à faire admettre que dix ans plus tard apparaîtront des microprocesseurs développant 0,5 Gips. Pourtant, en 1996 il existait déjà en laboratoire des microprocesseurs qui fonctionnaient à plus d' 1Gips.

#### 5 ABSORPTION DES GAMMES D'ORDINATEURS PAR LES MICROPROCESSEURS

Les ordinateurs qui utilisent des processeurs VLSI absorbent progressivement toutes les gammes d'ordinateur. L'absorption de la gamme des mini-ordinateurs s'est produite durant les années 80. Ces machines sont en passe d'absorber la gamme des ordinateurs de centre de calcul pendant les années 90. Vers 1993 les processeurs VLSI standards ont dépassés ceux des machines de centre de calcul en terme de complexité et de performance. Ils vont vraisemblablement absorber la gamme des super-ordinateurs dans le début des années 2000.

Figure 7 Absorption des gammes d'ordinateur par les microprocesseurs.

La production en grande série est nécessaire à la rentabilisation d'un circuit VLSI complexe (plus d'un million par an). Elle conduit nécessairement à la réduction du nombre de modèles différents. Par exemple les séries qui découleraient de la réalisation VLSI des processeurs des machines de centre de calcul ou des machines UNIX ne seraient pas assez importantes pour concurrencer les processeurs VLSI des ordinateurs individuels.

## 6 LES MICROPROCESSEURS CHANGENT NOTRE ENVIRONNEMENT

Les microprocesseurs jouent un rôle de plus en plus important dans la société. Ils peuvent être classés en deux groupes: Les "visibles" qui sont utilisés pour construire les différents modèles d'ordinateurs, surtout les modèles individuels, et les "invisibles" qui sont utilisés pour conduire et surveiller des machines outils, des automobiles, des avions, des appareils électroniques et de nombreux autres équipements électroniques. La famille des microprocesseurs invisibles est de loin la plus importante en terme numérique. Par l'intelligence qu'ils apportent, ces composants sont en train de changer progressivement la relation que nous avons avec les objets qui les utilisent.

Nous pouvons nous demander où ce phénomène nous entraîne. Les microprocesseurs sont en train de changer insidieusement notre environnement en rendant intelligent de nombreux objets qui étaient autrefois "simples" (automobile, téléphone,...). Pour un prix modique, il est maintenant possible de mettre un peu d'intelligence dans de nombreux objets et d'en transformer ainsi l'usage. Nous ne sommes actuellement qu'au début de cette profonde mutation de notre environnement.

# 7 L'HERITAGE DES ORDINATEURS

Tout au long de leur extraordinaire histoire, les processeurs VLSI ont réutilisé toutes les innovations techniques qui ont été développées pour les gammes précédentes d'ordinateur telles que: architectures pipeline, caches, architectures superscalaires, RISC, exécution dans le désordre, prédiction des branchements, etc.... Tous ces dispositifs sont maintenant utilisés dans les processeurs VLSI modernes qui sont actuellement les processeurs les plus avancés disponibles sur le marché. Ceux-ci sont devenu les descendants de l'histoire technique des ordinateurs. Pour maintenir le rythme de leur évolution il devient nécessaire de découvrir de nouvelles techniques pour accroître encore leur performances.

Les processeurs VLSI sont devenus les composants principaux des ordinateurs. Bâtir un processeur avec une technologie MSI est maintenant complètement dépassé et loin en dehors de l'optimum économique. Maintenant, tous les nouveaux ordinateurs sont basés sur l'utilisation de processeurs VLSI (Par exemple le super-ordinateur CRAY T3E utilise des microprocesseurs ALPHA).

#### 8 LES MICROPROCESSEURS VUS COMME DES CIRCUITS VLSI

Les microprocesseurs sont évidement des circuits VLSI. Dans de tels composants le circuit lui-même définit un monde interne qui est beaucoup plus petit et rapide que l'extérieur. Les capacités y sont mesurées en ff, les intensités en  $\mu a$ , les dimensions en  $\mu m$  et les retards en ps. Les portes internes de ces circuits intégrés fonctionnent beaucoup plus vite que celles des circuits MSI.

Pour un signal, le coût de passage du monde interne d'un circuit intégré VLSI au monde externe est très élevé. Des amplificateurs multi-étages et un adaptateur géométrique constitué par le boîtier sont nécessaires. La différence géométrique et électrique entre ces deux mondes est comparable au pilotage d'organes électromécaniques à partir d'une carte électronique.

Ce coût conduit les concepteurs de circuits VLSI à mettre le maximum de blocs fonctionnels dans un seul circuit au lieu d'utiliser des architectures multi-boitiers qui multiplient les (coûteuses) interfaces. Cet effet conduit à accroître le niveau d'intégration et la complexité des circuits.

Un autre paramètre important est la notion de distance sur le circuit VLSI lui-même. A son échelle, un circuit VLSI est un monde très grand! Nous pouvons comparer ces circuits avec un pays de 600km de large (c.a.d plus grand que la Suisse et la Belgique réunis) parcouru par des routes de 10m de large. L'organisation d'une telle surface demande d'utiliser des notions d'architecture (voire d'urbanisme). A titre d'exemple, les différents blocs constituant le dessin d'un tel circuit doivent s'imbriquer et s'interconnecter le mieux possible. Leur dessin doit donc être réalisé en conséquence.

Figure 8 Un circuit vu comme un pays.

Le coût de transfert de l'information d'une extrémité à l'autre d'un même circuit est très élevé. Les interrelations entre les différents blocs doivent donc être minutieusement étudiés pour accroître les échanges locaux et diminuer les communications à longue distance.

#### 9 LES PROCESSEURS VUS COMME DES INTERPRETEURS

Un processeur peut être vu comme un interpréteur de son langage d'instruction. Son algorithme d'interprétation est exécuté par le matériel et éventuellement aussi par un microprogramme. De nombreuses astuces sont utilisées pour accélérer son exécution, principalement en augmentant le parallélisme (les superpositions) dans son exécution.

Tous les processeurs déroulent un algorithme d'interprétation pour exécuter leurs instructions. D'autres types de circuits VLSI exécutent d'autres algorithmes tels que ceux du traitement du signal (ex. filtrage digital), de l'échange de données, de fonctions mathématiques,... Ils ne sont pas appelés des microprocesseurs mais leur structure interne est très voisine.

L'organisation fonctionnelle d'un processeur est typiquement découpée en deux unités fonctionnelles principales appelés: partie commande et chemin de données. Les spécifications de ces deux unités découlent de la décomposition de l'algorithme d'interprétation en son schéma d'enchaînement et en les opérations qu'il invoque. Le schéma d'enchaînement est utilisé pour spécifier la partie commande tandis que l'ensemble des opérations invoquées est utilisé pour spécifier le chemin de données.

Depuis le microprocesseur Motorola 6800 mis sur le marché en 1974, ces deux unités fonctionnelles sont réalisées par deux blocs de dessin séparés, conçus avec des techniques spécifiques.

#### 10 CONCEPTION DU CHEMIN DE DONNEES

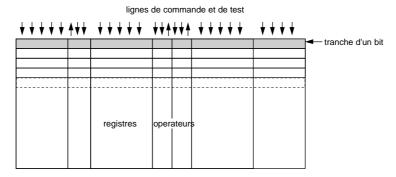

Le chemin de données est constitué d'opérateurs, de bus et de registres. Des techniques très efficaces sont maintenant utilisées pour le dessiner. La technique de base pour concevoir un chemin de données est l'utilisation de l'approche par tranches. Un dessin rectangulaire est obtenu par la juxtaposition et la duplication de bandes de dessin qui représentent un bit du chemin de données. Ces bandes sont constituées de l'assemblage de cellules qui ont une hauteur fixe. Les bus sont intégrés dans le dessin de ces cellules qui s'interconnectent par leur simple juxtaposition.

Figure 9 Organisation du dessin d'un chemin de données.

Le dessin d'un chemin de données est obtenu par l'utilisation d'outils de CAO appelés assembleurs de silicium. Ces outils effectuent l'assemblage des différentes cellules constituant le chemin de données. Certains de ces outils effectuent le redimensionnement automatique de certains transistors, ajoutent un réseau de distribution des alimentations ainsi que la ligne des amplificateurs de signaux de commande située sur le bord du chemin de données.

Le dessin final est très dense et optimisé. Le chemin de données constitue certainement la plus belle pièce de dessin d'un processeur VLSI. Sa surface est comprise entre le quart et la moitié de celle de tout le circuit.

# 11 CONCEPTION DE LA PARTIE COMMANDE

Malheureusement, il n'existe pas de technique globale pour concevoir les parties commande. Elles ne représentent pas vraiment des blocs de dessin mais des assemblages de modules séparés tels que des ROM, des PLA, des décodeurs et de la logique non structurée. Le dessin des parties commande est obtenu par l'utilisation des techniques classiques de placement-interconnexion.

Il existe plusieurs approches architecturales pour concevoir les parties commandes. Certaines d'entre elles sont directement inspirées des techniques de conception des ordinateurs traditionnels (MSI). Toutefois, l'opportunité de pouvoir concevoir les modules directement au niveau VLSI ouvre d'intéressantes perspectives.

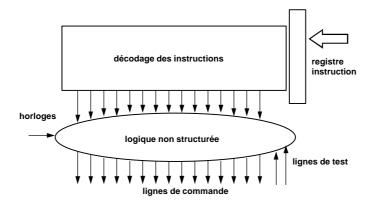

La partie commande d'un processeur VLSI peut être câblée ou microprogrammée. Une partie commande câblée est conçue autour d'un PLA (Programable Logic Array) qui effectue le décodage des instructions. Des chaînes de portes logiques sont utilisées pour valider les sorties de ce décodage par des signaux d'horlogerie, issus du générateur d'horloges du circuit, pour obtenir les commandes du chemin de données.

Figure 10 Partie commande câblée.

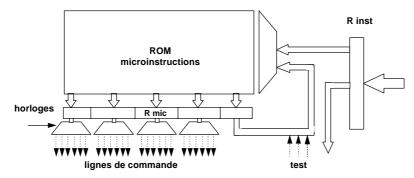

Une partie commande microprogrammée est organisée autour d'une ROM qui contient les microinstructions. Un compteur d'adresse de microinstruction est utilisé pour adresser cette ROM. Les microinstructions sont extraites de la ROM vers un registre de microinstruction dans lequel leurs différents champs sont décodés. Les commandes du chemin de données sont obtenues par la validation des sorties de ce décodage par les signaux d'horlogerie.

Figure 11 Partie commande microprogrammée.

Les parties commande microprogrammées sont mieux adaptées à l'exécution des instructions complexes dont l'exécution nécessite un nombre variable de cycles d'horloge. Cette technique est très utilisée par les microprocesseurs CICS.

Les parties commande câblées sont plus adaptées à l'exécution des instructions simples utilisant un nombre fixe de cycles d'horloge. Elles sont utilisées dans la conception des microprocesseurs RISC.

Ces deux types de parties commande utilisent aussi des blocs de logique non structurée qui sont réalisées sous la forme de bandes de cellules interconnectées via des canaux de câblage en utilisant les techniques développées pour la conception des circuits dits pré-caractérisés.

# 12 PROCESSEURS RISC

En 1975 un certain John Cocke a inventé la notion de processeur RISC (Reducted Instruction Set Computer) Dans un laboratoire de recherche d'IBM. Dans un processeur "classique" appelé CISC (pour Complex Instruction set Computer) l'utilisation des instructions est très déséquilibrée. A titre d'exemples, le taux d'utilisation des instructions de rupture de séquence est d'environ 25% tandis que celui des instructions qui manipulent des chaînes de caractères est loin en dessous de 1%. En ne conservant que les instructions les plus utilisées, les processeurs RISC sont mieux optimisés et les taux d'utilisation de leurs constituants matériels peuvent être équilibrés. Plusieurs caractéristiques sont spécifiques aux processeurs RISC:

- Un grand nombre de registres sont utilisés pour réduire le nombre d'accès mémoire.

- Très peu de formats d'instruction sont utilisés de manière à simplifier le décodage.

- Toutes les instructions (à l'exception de celles qui servent à effectuer des accès mémoire) sont exécutées dans le même nombre de cycles d'horloge de manière à simplifier le séquencement de leur exécution.

- Les accès mémoires sont effectués par quelques instructions spécifiques (qui n'effectuent que de simples transferts entre la mémoire et les registres).

L'interface matérielle / logicielle d'un processeur RISC est à un niveau beaucoup plus bas que dans un processeur CISC. Le faible niveau de cette interface provient d'une part de la réduction de la complexité des fonctions exécutées par le matériel et d'autre part de l'augmentation de la complexité de celles exécutées par le logiciel. Les programmes exécutés par un processeur RISC sont en général plus longs que ceux pour un processeur CISC. Par contre, la simplicité des instructions RISC permet une très bonne optimisation du code par les compilateurs. Cette optimisation alliée au faible temps de cycle des processeurs RISC leur procure une performance globale meilleure que celle des CISC.

La complexité du matériel d'un processeur RISC est beaucoup plus faible que celle d'un CISC. La partie commande d'un processeur RISC est câblée donc plus rapide. Sa surface est à peu près la même que celle du chemin de données.

Bien que la famille de processeur la plus répandue soit un CISC (famille 80x86), pratiquement tous les autres processeurs VLSI sont des RISC.

#### 13 ACCELERATION DE L'EXECUTION

La pression économique qui pousse à l'augmentation continuelle des performances des processeurs VLSI conduit leurs concepteurs à trouver de nouvelles approches pour concevoir ces machines. Toutes les techniques d'accélération sont basées sur l'utilisation de superpositions dans l'exécution de l'algorithme d'interprétation de manière à démarrer l'exécution d'une nouvelle instruction avant que soit terminée celle des instructions qui la précèdent.

#### 14 EXECUTION PIPELINE

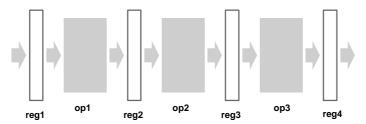

L'idée directrice de cette technique d'exécution est de découper le processus d'exécution d'une instruction en plusieurs sous-tâches exécutés par autant de modules matériels qui travaillent comme une chaîne de montage. Chacun de ces modules reçoit ses données (une instruction en cours d'exécution) dans ces registres d'entrées et met ses résultats dans ses registres de sortie. L'ensemble de ces registres constitue une file d'exécution dans laquelle les instructions sont progressivement exécutées. La complexité matérielle d'un processeur pipeline est plusieurs fois celle nécessaire pour une simple exécution séquentielle des instructions.

Figure 12 Structure matérielle d'un pipeline.

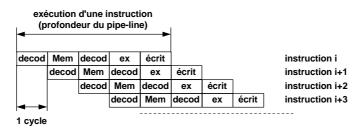

A chaque cycle d'horloge une nouvelle instruction entre dans le pipeline.

Figure 13 Instructions dans un pipe-line.

Le principal problème des architectures pipelines est celui des dépendances. Celles-ci peuvent être classées en deux familles principales:

• La première peut être appelée dépendance sur les données. Elle apparaît lorsqu'une instruction dans le pipeline veut lire une donnée qui n'a pas encore été calculée, l'élaboration de cette donnée devant être réalisée par une autre instruction plus loin dans le pipeline.

• La seconde peut être appelée dépendance sur les instructions. Elle apparaît lorsque la machine ne connaît pas la prochaine instruction à lire car le calcul de l'adresse de celle-ci dépend de la valeur de certaines conditions qui ne sont pas encore calculées.

Evidement, ces dépendances peuvent être résolues en arrêtant l'exécution de l'instruction qui pose problème (ainsi que de toutes les suivantes!) jusqu'à ce que la donnée ou la condition manquante soit calculée. Le coût de cette technique est assez élevé car des études statistiques montrent que la probabilité de rencontrer une telle dépendance croit fortement après seulement 3 instructions.

#### 15 REGISTRES VIRTUELS

Une solution élégante pour résoudre le problème des dépendances sur les données est d'utiliser des "registres virtuels". Dans les registres de la file d'exécution du pipeline les emplacements utilisés pour ranger les valeurs des opérandes peuvent être vus comme autant de registres virtuels qui peuvent être associativement adressés. Lorsqu'une instruction est en attente d'une donnée qui n'est pas encore calculée, l'emplacement où cette valeur sera rangée est vu comme un registre virtuel et la lecture en mémoire de cette donnée est supprimée. Lorsque l'instruction qui doit calculer cette donnée l'a élaborée, elle est alors chargée en parallèle dans les différents registres virtuels des instructions qui l'attendent en même temps qu'elle est rangée à sa place dans la mémoire. Ce court-circuit de l'accès mémoire et l'élimination de nombreuses lectures en mémoire augment les performances de la machine.

#### 16 PREDICTION DES BRANCHEMENTS

L'effet des dépendances sur les instructions peut être réduit en faisant des hypothèses sur le comportement des instructions de rupture de séquence conditionnelles. Meilleures seront les hypothèses, plus faible sera la dégradation de performance. Lorsqu'une telle hypothèse s'avère fausse, toutes les instructions qu'elle a permis de charger dans le pipeline doivent être éliminées. Pour permettre un tel retour arrière, toute les instructions qui sont lues à partir d'une telle hypothèse sont marquées comme conditionnelles. Ces instructions ne sont pas autorisées à modifier l'état visible de la machine (c.a.d. écrire dans les registres visibles et dans la mémoire).

De nombreuses techniques sont utilisées pour prédire le comportement des instructions de rupture de séquence conditionnelles. Nous allons distinguer entre les techniques statiques et les techniques dynamiques.

#### 17 TECHNIQUES STATIQUES DE PREDICTION

Les techniques statiques de prédiction sont très simples:

- La première consiste tout simplement à ne prendre aucun branchement conditionnel. Sa probabilité de succès est d'environ 40%. Elle a été utilisée dans le processeur VLSI 486.

- La seconde consiste à prendre tous les branchements conditionnels. Sa probabilité de succès est d'environ 60%.

- Une amélioration de la technique précédente consiste à prendre uniquement les branchements en arrière et à ne pas prendre ceux en avant (Elle est appelée BTFN pour Backward Take Forward Never). Sa probabilité de succès est de 65%. Elle est utilisée dans les processeurs VLSI Micro-Sparc 2 et PA RISC 7x00.

- Une autre technique, qui fut utilisée dans la machine Ridge, consiste à ajouter un bit à l'instruction de branchement. Ce bit est positionné par le compilateur pour indiquer si la meilleur hypothèse consiste à prendre ou à ne pas prendre le branchement. La probabilité de succès de ce mécanisme est d'environ 75%.

# 18 TECHNIQUES DE PREDICTION DYNAMIQUES

Les techniques de prédiction dynamiques consistent à mesurer le comportement de chaque branchement pour en déduire la meilleure hypothèse:

- La première technique fut développée par James Smith en 1981. Elle consiste à enregistrer le comportement de chaque branchement conditionnel de manière à prédire le dernier comportement. Evidement la taille de la table utilisée est limitée et seulement le comportement des dernières instructions de branchement peut être enregistré. La probabilité de succès de cette technique est d'environ 80%. Elle est utilisée dans les processeurs VLSI ALPHA et K5.

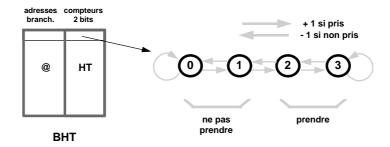

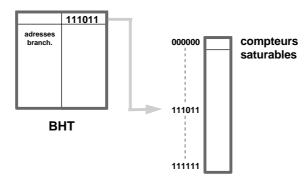

- Une évolution de la technique précédente est appelée BHT (pour Branch History Table). Elle utilise un compteur saturable comme un élément d'inertie pour mesurer le comportement de chaque instruction de branchement conditionnel. Sa probabilité de succès devient 85%. Cette technique est utilisée dans de nombreux processeurs VLSI: PPC 604-620, ALPHA, Nx586, Ultra Sparc, M1, Pentium.

Figure 14 Table BHT.

• Un mécanisme à deux niveaux a été proposé par Yeh et Patt en 1991. Cette technique consiste à enregistrer les comportements successifs de chaque instruction de branchement conditionnel. En complément, un compteur saturable est utilisé pour prédire le futur de chaque profil de comportement. La probabilité de succès devient très élevée (95%). Cette technique est utilisée dans le processeur VLSI Pentium Pro.

Figure 15 Mécanisme dynamique à deux niveaux.

# 19 AUTRES TECHNIQUES COMPLEMENTAIRES

Comme la bonne prédiction du comportement des branchements est très importante en termes de performance, d'autres mécanismes sont aussi utilisés:

- L'enregistrement des adresses des branchements calculés dans une table associative.

- L'utilisation d'une pile matérielle pour enregistrer les adresses de retour des sous-programmes et des interruptions (en plus de la pile système située en mémoire). Cette technique est utilisée dans les processeurs VLSI M1 et ALPHA.

- L'utilisation d'un tampon alternatif appelé BTC (pour Branch Taken Cache) pour pré-charger et pré-décoder les premières instruction des voies alternatives.

#### 20 SUPER-PIPELINE

L'efficacité des techniques pour réduire les inconvénients des dépendances conduit les concepteurs de processeurs VLSI à augmenter la longueur des pipelines pour diminuer la quantité de travail réalisée dans chaque étage. Cette évolution architecturale permet de diminuer la période de l'horloge de la machine. Avec cette technique le débit d'instruction entrant dans le pipeline est augmenté. Le processeur démarre plus d'instructions par seconde et sa performance est augmentée (sous la réserve que le taux de dépendance n'ait pas ré-augmenté!). A titre d'exemple le processeur VLSI MIPS R 4000 utilise un pipeline à 8 étages.

## 21 SUPER-SCALAIRE

Une autre technique d'accélération consiste à disposer plusieurs pipelines en parallèle de manière à augmenter le débit de traitement des instructions. Ces pipelines peuvent être identiques ou spécialisés. Certains processeurs utilisent un pipeline spécifique pour les instructions de traitement des entiers et un autre pour les instructions manipulant des nombres flottants. Dans ce cas, chaque pipeline s'alimente avec les instructions qu'il sait exécuter. Les pipelines spécialisés utilisent des ensembles de ressources (registres) différents. Il n'y a donc aucun problème de dépendance entre eux. Quand les pipelines sont identiques, ils partagent de nombreuses ressources. Des conflits et des dépendances peuvent alors apparaître. Dans ce cas, il est nécessaire d'étendre à l'ensemble des pipelines la notion de registres virtuels.

| Γ | LI | SP | DI | LO | EX1 | EX2 | RR  |    | 2 voies d'exécution identiques |  |

|---|----|----|----|----|-----|-----|-----|----|--------------------------------|--|

|   | LI | SP | DI | LO | EX1 | EX2 | RR  |    |                                |  |

|   |    | LI | SP | DI | LO  | EX1 | EX2 | RR |                                |  |

|   |    | LI | SP | DI | LO  | EX1 | EX2 | RR |                                |  |

|   |    |    |    |    |     |     |     |    |                                |  |

Figure 16 Les deux pipelines du processeur VLSI ALPHA.

A titr e d'exemple, le processeur VLSI ALPHA utilise deux pipelines identiques.

#### 22 EXECUTION DANS LE DESORDRE

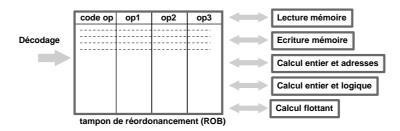

La technique d'accélération la plus puissante est l'exécution dans le désordre qui consiste à exécuter les instructions dès que possible sans attendre la terminaison des précédentes. Ce mécanisme d'exécution est organisé autour d'un tampon particulier appelé ROB (pour ReOrdering Buffer). Dans ce tampon les instructions sont progressivement exécutées ("construites") par des opérateurs spécialisés. Un opérateur d'alimentation charge les instructions dans le ROB, détecte les dépendances sur les données et les résout en utilisant la technique des registres virtuels. Dans le ROB les instructions ont un format beaucoup plus grand que celui qu'elles ont en mémoire. Ce format contient des champs spécifiques pour y ranger les valeurs des opérandes et des résultats. Tous les autres opérateurs scrutent indépendamment le ROB pour y trouver des instructions qu'ils peuvent faire progresser (indépendamment de leur position dans le programme). Par exemple l'opérateur chargé de la lecture des opérandes en mémoire cherche des instructions qui ont besoin de lire des données en mémoire. Cet opérateur lit ces données et les charge dans les champs correspondants dans le ROB. Il y a plusieurs opérateurs spécialisés pour l'exécution (entiers, flottants, chaînes de caractères, calcul d'adresses,..). Chacun d'eux cherche dans le ROB des instructions qui possèdent toutes leurs données. Lorsqu'un opérateur en trouvent une, il calcule son résultat et le met dans le ROB. Cet opérateur charge le résultat dans le champ résultat de l'instruction qu'il est en train d'exécuter mais aussi dans tous les registres virtuels qui l'attendent. L'opérateur de rangement cherche les instructions dont le champ résultat est garni. Lorsqu'il en trouve une, il charge le contenu de ce champs en mémoire et efface l'instruction du ROB.

Figure 17 Mécanisme d'exécution dans le désordre.

Cette technique d'exécution très puissante, mais aussi très coûteuse, est utilisée dans le processeur VLSI Pentium Pro.

# 23 TRADUCTION CISC EN RISC

De manière à pouvoir bénéficier des avantages liés aux architecture RISC, les concepteurs de processeurs CISC ont imaginé une technique d'exécution qui consiste à décomposer chaque instruction CISC en une suite d'instructions RISC. Ces instructions RISC sont chargés dans le ROB et exécutés dans le désordre. Le processeur VLSI Pentium Pro utilise cette technique.

## 24 UTILISATION DE TRES LONG MOTS D'INSTRUCTION (VILW)

Dans les ordinateurs VILW, plusieurs instructions élémentaires (supposées sans dépendance) sont groupées dans un mot très long terminé par une instruction de branchement. Ces instructions groupées sont exécutées en parallèle par plusieurs voies matérielles d'exécution. Dans ces ordinateurs, les mots longs sont préparés par le compilateur qui évite les dépendances. Dans les ordinateurs classiques il semble possible de construire dynamiquement de tels mots longs par un module spécialisé, interfacé avec l'antémémoire interne, pour alimenter plusieurs voies d'exécution parallèles.

#### 25 AMELIORATION DES ACCES MEMOIRES

Les temps d'accès des mémoires ne décroissent pas aussi vite que les temps de cycle des processeurs.

Les processeurs RISC minimisent cet effet en utilisant de nombreux registres pour réduire le nombre des accès mémoire.

Les processeurs CISC font de nombreux accès mémoire. Ils doivent donc impérativement utiliser une hiérarchie performante d'antémémoires pour masquer la lenteur relative de la mémoire.

La mémoire et les registres sont des ressources uniques qui introduisent des goulots d'étranglement. L'utilisation de registres virtuels diminue le débit processeur - mémoire.

#### 26 HIERARCHIE MEMOIRE

Tous les nouveaux processeurs VLSI utilisent plusieurs niveaux d'antémémoires (caches) pour accélérer leurs accès mémoire. Ils possèdent tous une ou deux antémémoires intégrées directement sur leur circuit. Le fait de mettre une antémémoire sur le circuit la met dans le même monde microscopique que le processeur. La communication entre ces deux organes peut se faire beaucoup plus rapidement et surtout le nombre de connexions qui les relient peut être très important. De nombreux processeurs VLSI possèdent deux antémémoires intégrées. Une pour les données et une pour les instructions. Leur stratégies de gestion peuvent être adaptées à ces deux types d'information.

Comme la taille des antémémoires intégrées est relativement faible, leur taux de succès est relativement bas. Un second niveau d'antémémoire de taille plus importante est alors nécessaire. Celui-ci est alors soit disposé sur la carte mère soit dans le même boîtier que le processeur (par exemple le Pentium Pro). Vraisemblablement l'évolution des processeurs VLSI va conduire à augmenter fortement la taille de l'antémémoire intégrée.

#### 27 MULTIPROCESSEURS MONOLITHIQ UES

Puisque les processeurs VLSI ont déjà réutilisé toutes les techniques connues d'accélération de l'exécution, plusieurs auteurs suggèrent le développement de multiprocesseurs monolithiques. Cette idée n'est pas spécialement nouvelle et déjà plusieurs projets de tels multiprocesseurs ont déjà été envisagés (Par exemple un projet de double MC 6800 a été envisagé à la fin des années 70). Malheureusement pour ces projets, les nouvelles générations de (mono) processeurs VLSI se sont montrés plus attractifs et ils furent abandonnés. Maintenant la situation a peut être un peu changé puisque pratiquement toutes les techniques d'accélération des monoprocesseurs ont été exploitées.

Il est possible d'imaginer ce que pourrait être un duo monolithique de processeurs. Plusieurs grands systèmes d'exploitation: UNIX, Window NT, ... sont déjà prêt à les utiliser efficacement. Une autre solution serait de les spécialiser, par exemple l'un pour le système, les entrées sorties, la visualisation et l'autre pour les tâches de l'utilisateur.

Le taux d'utilisation de ces processeur pourrait devenir momentanément très bas, mais cela n'a pas une grande importance. Le développement de l'informatique individuelle s'est faite au prix d'une sous-utilisation flagrante des ressources matérielles. Par exemple un ordinateur de centre de calcul est conçu et optimisé pour optimiser l'utilisation de ses ressources matérielles. Dans un PC, l'utilisation de ces ressources est très peu optimisé (par exemple l'ordinateur ne sert à rien lorsque son utilisateur est absent) mais le résultat est très intéressant sur un plan économique.

# 28 CONCLUSIONS

L'évolution des processeurs VLSI est l'une des plus excitantes histoires techniques de la fin de ce siècle et probablement du début du prochain. La puissance de traitement de ces circuits à été multipliée par un facteur de plusieurs milliers dans les 25 dernières années. Aucun autre domaine technique n'a eut une telle évolution.

Les processeurs VLSI sont en train de se substituer à toutes les autres technologies de construction des processeurs. Probablement ils vont se substituer aux super-ordinateurs dans les toutes premières décennies des années 2000.

Aujourd'hui ces machines peuvent être vues comme des regroupement de plusieurs sous-processeurs coopérant à l'exécution d'un seul programme. Vraisemblablement, ces circuits vont contenir plusieurs processeurs qui travaillerons en parallèle sur plusieurs tâches.

Nous pouvons aussi nous poser la question de savoir où une telle évolution nous mène. Les puissances de calcul qui se profilent à l'horizon sont très impressionnantes. Elles vont ouvrir à tout le monde l'utilisation des technologies de simulation, de CAO, de la réalité virtuelle, etc... faisant de l'ordinateur individuel le meilleur des outils.

## 29 BIBLIOGRAPHIE

- [1] Anceau, F. (1986) The Architecture of Microprocessors. Addison-Wesley.

- [2] Tredennick, N. (1986) Microprocessor Logic Design, Digital Press.

- [3] Hennessy, J.L. and Patterson, D. A. (1990) Computer Architecture a Quantitative Approach, Morgan Kaufmann. traduction: Architecture des ordinateurs, une approche quantitative, Thomson publishing.

- [4] Richard Comerford (1992) How DEC developed Alpha, IEEE Spectrum, July 1992

- [5] Milutinovic, V. (1996) Surviving the Design of a 200 Mhz RISC Microprocessor, Lessons Learned. Computer Society.

On trouvera de nombreuses informations au sujet de l'architecture des processeurs VLSI dans la lettre Microprocessor Report et dans les actes du congrès ISSCC.